摘要

IEEE1588标准又称为网络测量和控制系统的精确时钟同步协议标准,是IEEE标准委员会颁布的为了满足定位服务和无线移动通信系统高精度同步要求的标准。随着Ethernet技术的广泛应用,采用IEEE1588方式通过以太网实现时钟同步方案在网络上的应用越来越普遍。本文简要介绍1588的原理和常见的实现方式,并详细介绍TI KeyStone架构上的1588实现方案。

1 概述

1588是IEEE规范定义的网络实时同步标准[1]。它提供一种通过网络信息交互以获得精准时钟信息的标准。和在广域网上的NTP协议比较,1588最新标准提供高于纳秒级别的时钟精度,可以用来满足要求在一个相对小的空间范围内对时钟同步有严格要求的应用场景,例如基站同步,音视频网桥(AVB),工业控制,产线控制,军事应用等。

KeyStone架构是TI推出的高性能多核架构,该架构目前已演进了两代——KeyStone1 和KeyStone2。基于KeyStone架构,TI推出多款针对基站和网络应用的多核芯片。

KeyStone1家族基于40nm工艺,包括如下器件型号:

- TCI6616,参见文献[2]

- TCI6618,参见文献[3]

- TCI6614 和TCI6612,参见文献[4]和[5]

- TMS320C6678、TMS320C6674、TMS320C6672 等,参见文献[6]

KeyStone2家族基于28nm工艺,包括如下器件型号:

- TCI6636K2H,参见文献[7]

- TCI6634K2K,参见文献[8]

- TCI6638K2K,参见文献[9]

- TCI6630K2L (即将发布),参见文献[10]

本文首先介绍IEEE1588的基本原理,然后以常见的基于PHY的IEEE1588实现方案为参考,介绍KeyStone架构上支持IEEE1588的硬件功能。同时,本文总结了在KeyStone1芯片上实现IEEE1588方案需要注意的实现细节,并对KeyStone2芯片的1588方案做初步介绍。

2 IEEE1588时钟同步原理

IEEE1588使用精准时间协议PTP(Precision Timing Protocol),通过端到端的报文交互获得时钟参考信息,矫正本地时钟频率和相位。1588协议基于两个假设条件:第一,在时钟源设备和受时钟设备之间,网络报文传输时间是对称的。也就是说一个报文从时钟源设备到受时钟设备的传输时间等于报文从受时钟设备到时钟源设备的传输时间相同;第二,在PTP报文交换过程当中,本地时钟的漂移可以忽略不计。

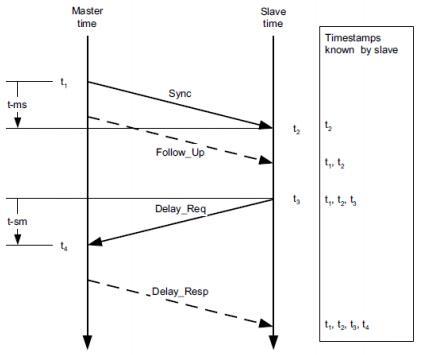

图1:IEEE1588时钟同步原理

如图所示,在经过sync->delay_request->delay_response消息交互以后,受时钟设备获得4个时间值。以太网报文在两个设备之间的环路时延可以计算为:

Troundtrip=(t4-t1)-(t3-t2)

假设包传输时延是对称的,那么单路时延是:

Ttripdelay=((t4-t1)-(t3-t2))/2

从时钟设备的时钟和主时钟的差值是:

Tdelta=t2-(t1+Ttripdelay)

实际部署时,时钟源发送sync消息,从设备根据多个sync消息来计算本地时钟的偏差。当从设备需要同步本地时钟相位的时候,发送delay_req消息,时钟源发送delay_response,从设备根据获得的4个时间值来估计相位的偏差。

对于时钟源设备,如果在发送sync报文时所带的时间戳就是报文发送时采集的准确时间,这种模式叫做single step模式。如果发送sync报文的时候所带的时间戳只是一个近似时间,sync报文发送的准确时间不能在发送sync报文的时候获得或者实时插入到sync报文中,时钟源设备需要发一个follow up消息报文,用来传递sync 报文的准确发送时间,这种模式叫做two step模式。下面介绍的PHY 方案支持时钟源single step,TI的KeyStone架构支持时钟源two step模式。

3 1588芯片实现方案

根据打时间戳的方式不同,常见的1588方案分为软件时间戳方案和硬件时间戳方案。软件方案通常是通过软件手段在网络报文的接收中记录PTP报文接收或发送时间,处理灵活,可以根据应用场景灵活处理PTP协议报文,支持多种封装格式。但是因为软件中断的时间抖动大,软件时间戳方案的精度较差,在对精度要求不高的情况下使用。硬件方案通过特殊硬件解析PTP 报文,并用硬件记录报文发送或接收时间。硬件方案精度高,但是需要特殊硬件解析PTP报文,在特殊场景中,例如PTP over IPSec,报文经过加密,硬件无法解析PTP报文。根据硬件方案获取报文收发时间地点不同,硬件方案又分在PHY上集成的1588方案和MII集成的1588方案等。

下面先简单介绍一下TI基于PHY的硬件解决方案作为参考,然后着重介绍KeyStone架构上的基于MII和PA的1588 方案。

3.1 以太网PHY1588方案(DP83640)

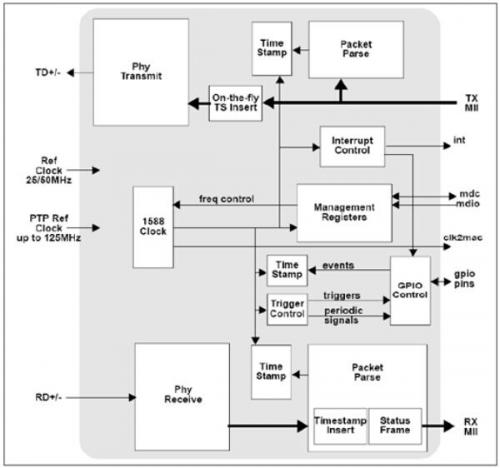

图2:DP83640高精度时钟同步硬件模块

DP83640[11]是一款百兆网口PHY,集成1588功能,对外提供校准过的时钟和PPS信号,同时还支持同步以太网功能,直接从物理层获得远端时钟。在支持同步以太网的情况下,使用1588做相位调整,实验表明最终的时钟偏差精度可以达到纳秒以下。

83640 timestamp模块维护一个本地的1588计数器,包括32bit的秒计数和30bit的纳秒计数。PTP报文中要求的48bit秒计数中的高16位需要软件维护。上层软件在发送一个1588报文的时候,时间戳中秒计数的高16位由软件设置的,低32位设置为0。

报文解析模块用来匹配解析PTP报文。83640支持1588Annex D&E和Annex F格式的报文。当PTP报文送至PHY时,报文解析硬件检测到这个PTP报文的时钟,在报文发出时,把本地的时间戳写到PTP报文里面,并修改相关的CRC 和CHKSUM值。83640支持1588 single step模式的时钟源。在报文接收方向,同样有报文解析硬件。在解析到PTP报文以后,接收报文的准确时间戳可以插入在报文里,或者通过控制接口上报。

83640的1588时钟模块对外提供频率控制接口,软件通过控制寄存器可以调整输出的时钟频率。1588时钟模块根据上层软件的配置,对1588时钟模块的输入时钟信号微调,然后分频输出。时钟调整是通过调整每个时钟周期的时间来实现的。在每个时钟周期调整的单位是2-32ns。在正常模式下,这个调整机制用来补偿本地时钟和时钟源的差距。在长期工作以后产生累积同步误差时,软件可以调整寄存器的值,在一定时间内,对频率向上或者向下微调,以补偿相位差距。当在相位补偿以后,恢复正常频率补偿模式。

软件协议栈通过协议处理以后获得本地的时钟与时钟源的绝对时间差值,然后通过寄存器调整本地绝对时间戳。在修改时,软件把绝对时间差值写入寄存器,然后使能修改。这种方法适用初始同步时单次校正本地绝对时间戳。如在正常工作中出现累积相位偏差,应该使用前面介绍的微调方法,避免输出时钟抖动。

应用层通过设置83640的trigger control模块来控制输出PPS 或者其他同步信号。应用可以设置在timestamp 的哪些具体时刻某个GPIO管脚可以发生反转。trigger的输出可以线与并输出到GPIO管脚,通过线与可以是输出复杂的周期波形。

83640方案实现简单,直接输出矫正时钟及相位信号,但是对于复杂传输场景支持困难;而且相比不包含IEEE1588功能的PHY芯片,83640的成本要高出许多。

3.2 KeyStone1 1588方案

KeyStone架构是TI推出的高性能多核架构,现在已经有KeyStone1和KeyStone2两种架构。KeyStone架构中也包含了对IEEE1588功能的支持。

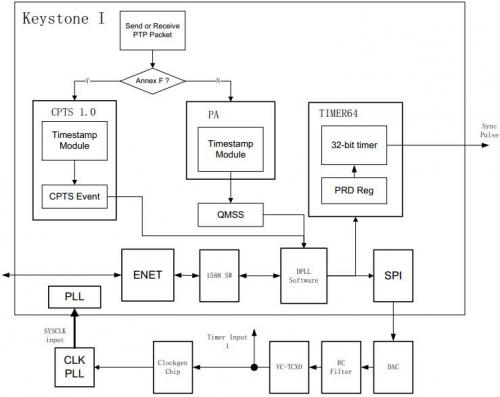

KeyStone1系列芯片的1588方案包括两个硬件部分:记录时间戳,发送同步脉冲。KeyStone1支持two step的时间戳模式,同时也能支持1588协议中Annex D&E和Annex F规定的PTP报文解析。

对于记录时间戳,KeyStone1对于Annex D&E和Annex F采用不同的硬件来支持。Annex D&E使用以太网协处理(NetCP)里面的包加速器(PA)来支持;Annex F报文使用以太网交换机(GE Switch)里面的CPTS模块来支持 [12-13]。

对于同步信号的输出,KeyStone1里面需要通过Timer64[14]来完成。软件通过CPTS或者PA获取到时间戳后,计算需要调整的频率和相位,然后通过配置Timer64的周期寄存器来更改Timer64的输出周期,调整输出的相位信息;通过SPI接口调整外部的VCXO的输出频率,矫正本地时钟频率。

图3:KeyStone1 IEEE1588时钟同步方案

3.2.1 Annex D&E PTP报文处理

PA内部会维护一个48bit的计时器,该计时器的频率与PA的频率一致(一般是350MHz)。由于Annex D&E报文的承载方式为IP/UDP承载(报文模式为IPv4和IPv6),当用户收到或者发送一个IPv4或IPv6的PTP报文时,在PA 侧会记录一个报文接收(或发送)的时间戳,这个时间戳只有32bit(为48bit中的低32bit)。这个时间戳保存在用户指定的QMSS的某个Queue的描述符里面。

用户从Queue中提取出该描述符:如果是接收,用户可根据描述符信息解析报文类型,获取报文内容,同时读取32bit时间戳并换算成绝对时间。如果是发送,用户只需读取时间戳,转换为1588 48bit绝对时间后按照1588 two step的规则再做报文发送。

3.2.2 Annex F PTP报文处理

GE Switch模块上的CPTS模块支持对1588 Annex F(以太网封装)的PTP报文解析,支持VLAN。在CPSW逻辑匹配到PTP报文时,会触发一个硬件信号给CPTS模块用来触发时间戳获取。

CPTS 的时间戳模块维护一个32bit的timer,根据配置,这个timer可以工作在二分之一CPU主频上。这个timer 是一个free run timer。软件通过这个timer换算得到1588的32bit纳秒时钟和48bit秒时钟。因为timer只有32bit,所以软件需要处理timer反转事件,用来维护秒信息。CPTS得到时间事件以后,会将PTP报文的消息类型和Sequence ID等信息压入EVENT FIFO中,并触发中断让用户处理。

3.2.3 同步信号的产生

同步信号需要通过Timer64来产生。由于Timer64,PA以及CPTS都是共用KeyStone外部的VCXO,因此从时间源上保证各个计时器之间没有累积误差。这样计算出来的各个绝对时间也是固定不变的。

关于同步信号的时间戳,有两点需要说明:

1.KeyStone芯片的1588功能不维护绝对时间戳,时间信息是从CPTS timer或者PA的timer换算出来。这样也不支持对1588报文发送时实时修改,所以在用KeyStone芯片做时钟源时,芯片只支持two step模式。

2.输出时钟方案需使用KeyStone1芯片上的定时器的输出。因为CPTS(或PA)上打时间戳的计数器和定时器使用的时钟虽然是同源,但是相位不同,产生的PPS时钟时,需要软件参与校正两个计数器,并对记录相应的相位差。具体实现时,需要首先对CPTS(或PA)里面的计数器和选定的Timer64计数器相差相位进行计算。软件首先操作CPTS(或PA)寄存器,触发一个CPTS时间戳记录事件(或者发起一个读取PA时间戳寄存器的命令),然后马上读取timer64的值。考虑到cache问题以及硬件总线上的竞争可能性,软件应在一个循环内多次执行这个操作,保证执行程序加载到L1 cache中,两个时钟之间的相位差应该可以通过循环几次获得的值平均得到。

3.3 KeyStone2 1588方案

KeyStone2架构的TI芯片对1588的支持做了改进和增强。CPTS模块支持同步以太网(Annex F)和1588 Annex D &E的报文。在KeyStone2芯片中,PPS输出是直接由CPTS逻辑驱动的。软件通过设置相关寄存器设置下一个PPS 输出时timestamp的值,当计数器跑到设置的值的时候,硬件触发PPS信号输出。

图4: KeyStone2 IEEE1588时钟同步方案

+86 4006 93 93 63 +86 10 6395 8133

+86 1338 137 0518

OUR CUSTOMERS

+86 10 6395 8139

info@ojumpo.com dglei-vp@126.com

北京市海淀区中关村南大街31号 神舟大厦七层